# Syllabus for B. Tech. Electronics And Communication Engineering

Digital System Design

Code: EC-302 Contacts: 3L Credits: 3

# Module I (10L)

Review of Number System, Signed and Unsigned Number.

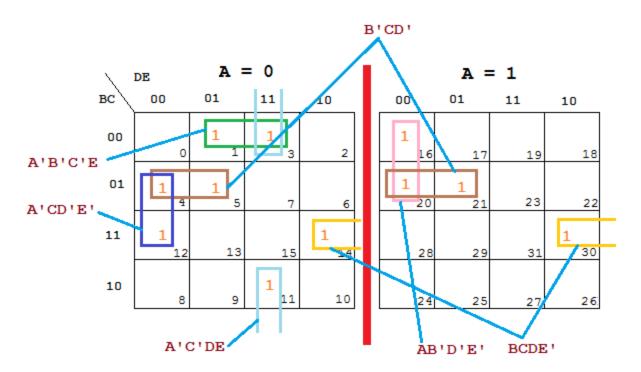

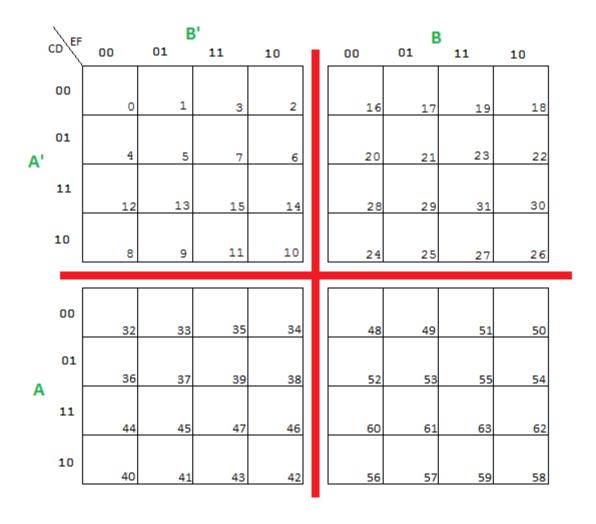

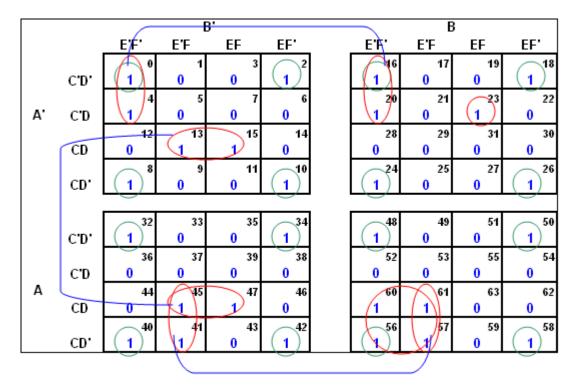

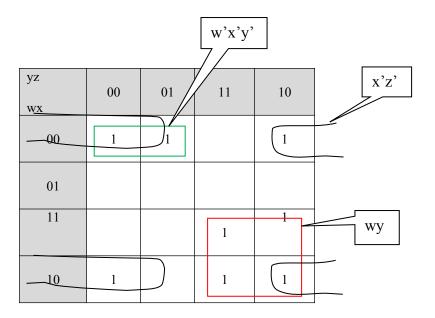

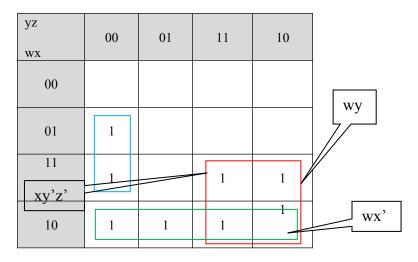

Logic Simplification and Combinational Logic Design: Review of Boolean Algebra and De-Morgan's Theorem, SOP & POS forms, Canonical forms, Karnaugh's map, Binary codes, Code Conversion.

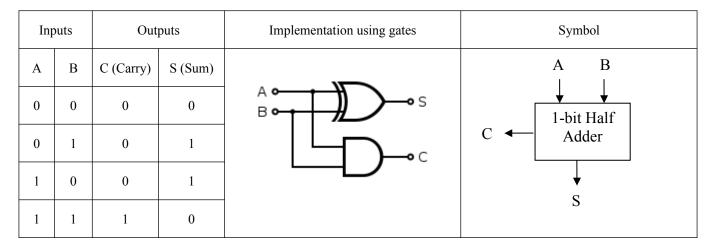

MSI devices like Comparators, Multiplexers, Encoder, Decoder, Half and Full Adders, Subtractors, Serial and Parallel Adders, BCD Adder, Fast adders, Barrel shifter and ALU.

#### Module II (6L)

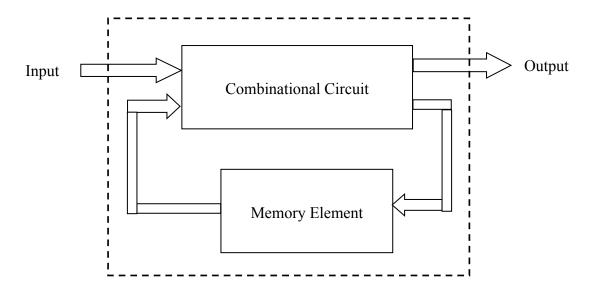

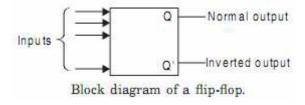

Ripple and Synchronous counters, Shift registers, Finite state machines, Design of synchronous FSM. Designing synchronous circuits like Synchronous Counter, Pulse train generator, Pseudo Random Binary Sequence generator.

#### Module III (8L)

Logic Families and Semiconductor Memories: TTL, ECL, CMOS families. Semiconductor Memories, Concept of Programmable logic devices like FPGA. Logic implementation using Programmable Devices.

Different types of A/D and D/A conversion techniques. Sample and hold circuit.

#### Unit IV (8L)

VLSI Design flow: Design entry Schematic, FSM & HDL, different modeling styles in VHDL, Data types and objects, Data flow, Behavioral and Structural Modeling, Synthesis and Simulation VHDL constructs and codes for combinational and sequential circuits.

# Text/Reference Books:

- 1. R.P. Jain, "Modern digital Electronics", Tata McGraw Hill, 4th edition, 2009.

- 2. Schilling & Belove, Digital Integrated Electronics, Tata McGraw Hill,

- 3. Douglas Perry, "VHDL", Tata McGraw Hill, 4th edition, 2002.

- 4. W.H. Gothmann, "Digital Electronics- An introduction to theory and practice", PHI, 2nd edition ,2006.

- 5. D.V. Hall, "Digital Circuits and Systems", Tata McGraw Hill, 1989

- 6. Charles Roth, "Digital System Design using VHDL", Tata McGraw Hill 2nd edition 2012.

- 7. R. Anand, "Digital Electronics", Khanna Publishing House, New Delhi, 2017.

#### **Course outcomes:**

At the end of this course students will demonstrate the ability to

- 1. Design and analyze combinational logic circuits

- 2. Design & analyze modular combinational circuits with MUX/DEMUX, Decoder, Encoder

- 3. Design & analyze synchronous sequential logic

# Lesion Plan, Digital System Design (EC302), Session 2023-24, ODD SEM

# Module-I (10L)

- Review of Number System (2L):

- Lec1: Unsigned Number 1L

- Lec2: Signed Number 1L

- Logic Simplification and Combinational Logic Design (5L):

- Lec3: Review of Boolean Algebra and De-Morgan's Theorem 1L

- Lec4: SOP & POS forms, Canonical forms 1L

- Lec5-6: Karnaugh's map 2L

- Lec7-8: Binary codes, Code Conversion 2L

- MSI devices like (3L):

- Lec9-10: Comparators, Multiplexers, Encoder, Decoder 2L

- Lec11-12: Half and Full Adders, Subtractors, Serial and Parallel Adders 2L lecture

- Lec-13: BCD Adder, Fast adders, Barrel shifter and ALU 1L

# Module-II (6L)

- Lec14: Ripple and Synchronous counters 1L

- Lec15: Shift registers 1L

- Finite state machines (4L):

- Lec16: Design of synchronous FSM 1L

- Designing synchronous circuits like:

- ◆ Lec17-18: Synchronous Counter 2L

- ◆ Lec19: Pulse train generator, Pseudo Random Binary Sequence generator 1L

#### Module III (8L)

- Logic Families and Semiconductor Memories:

- Lec20-21: TTL, ECL, CMOS families 2L

- Lec22: Semiconductor Memories 1L

- Lec23: Concept of Programmable logic devices like FPGA 1L

- Lec24: Logic implementation using Programmable Devices 1L

- Different types of A/D and D/A conversion techniques (3L):

- Lec25: Sample and hold circuit 1L

- Lec26: D/A Converters 1L

- Lec27: A/D Converters 1L

# Unit IV (8L)

- Lec28-29: VLSI Design flow: Design entry Schematic, FSM & HDL 2L

- Lec30-33: different modeling styles in VHDL, Data types and objects, Data flow, Behavioral and Structural Modeling 4L

- Lec34-35: Synthesis and Simulation VHDL constructs and codes for combinational and sequential circuits - 2L

#### Module-I:

NUMBER SYSTEMS: Binary, Octal and Hexadecimal representation and their conversions; BCD, ASCII, EBDIC, Gray codes and their conversions; Signed binary number representation with 1's and 2's complement methods, Binary arithmetic.

#### Introduction:

What is Electronics?

Electronics means study of flow of electrons in electrical circuits. The word Electronics comes from electron mechanics which means learning the way how an electron behaves under different conditions of externally applied fields. IRE - The Institution of Radio Engineers has given a definition of electronics as "that field of science and engineering, which deals with electron devices and their utilization." Fundamentals of electronics are the core subject in all branches of engineering nowadays.

Electronics is distinct from electrical and electro-mechanical science and technology, which deals with the generation, distribution, switching, storage, and conversion of electrical energy to and from other energy forms using wires, motors, generators, batteries, switches, relays, transformers, resistors, and other passive components. This distinction started around 1906 with the invention of the triode by Lee De Forest, which made electrical amplification of weak radio signals and audio signals possible with a non-mechanical device. Until 1950 this field was called "radio technology" because its principal application was the design of radio transmitters, receivers, and vacuum tubes.

Analog electronics are electronic systems with a continuously varying signal, in contrast to digital electronics where signals usually take only two different levels. The term "analogue" describes the proportional relationship between a signal and a voltage or current that represents the signal. The word analogue is derived from the Greek word "Analogos" meaning "proportional".

# BINARY NUMBER SYSTEM

We are comfortable with Decimal Number System having base or radix of 10. Implementation of decimal system in digital circuits thus requires signals (voltage/current) to be divided into 10 levels. The same reduces the reliability of the system giving birth of binary system which uses only two levels - logic 0 and logic 1. In digital circuits, logic 0 is represented by 0V and logic 1 is represented by 5V.

Binary number system is also a positional weighted system like decimal number system where each binary digit (called bit) carries a certain weight according to its position with respect to the decimal point as shown below:

Table-1: Weights of the bits of a binary number with 8-bit integer and 4-bit fraction.

| Bit    | d <sub>7</sub> | d <sub>6</sub> | d <sub>5</sub> | d <sub>4</sub> | d <sub>3</sub> | d <sub>2</sub> | $d_1$          | d <sub>0</sub> | • | d <sub>-1</sub> | d <sub>-2</sub> | d <sub>-3</sub> | d <sub>-4</sub> |

|--------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|---|-----------------|-----------------|-----------------|-----------------|

| Weight | 27             | 2 <sup>6</sup> | 25             | 24             | 2 <sup>3</sup> | 2 <sup>2</sup> | 2 <sup>1</sup> | 20             | • | 2-1             | 2-2             | 2-3             | 2-4             |

| weight | 128            | 64             | 32             | 16             | 8              | 4              | 2              | 1              | • | 0.5             | 0.25            | 0.125           | 0.0625          |

Example1: Convert 110100<sub>b</sub> to its equivalent decimal

\_\_\_\_\_\_  $110100_{b} = 1x2^{5} + 1x2^{4} + 0x2^{3} + 1x2^{2} + 0x2^{1} + 0x2^{0}$ = 32 + 16 + 0 + 4 + 0 + 0

# Example-2: Convert 110.101<sub>b</sub> to its equivalent decimal

\_\_\_\_\_\_

```

110.101_{b} = 1x2^{2} + 1x2^{1} + 0x2^{0} + 1x2^{-1} + 0x2^{-2} + 1x2^{-3}

= 4 + 2 + 0 + 0.5 + 0 + 0.125

= 6.625_{d}

```

These examples illustrate binary to decimal conversion. Decimal to binary conversion is as follows:

- First divide the number at the decimal point and treat the two parts separately

- For the integer part, repeatedly divide it by 2 and store the remainder until nothing is left

- Write the remainders from bottom to top to get the binary number. The reverseordering comes as the first division by 2 gives the *least significant bit* (lsb) and so on until the last division which gives the *most significant bit* (msb).

- For the fractional part, repeatedly multiply the fraction part by 2 and record the carries i.e. when the resulting number is greater than 1. Repeat this process until the desired precision is achieved.

# Example-3: Convert $57.4801_d$ to its binary equivalent to 14-bit accuracy.

\_\_\_\_\_\_

As the decimal number has both an integer and a fractional part the problem has to be done in two steps

First take the integer part i.e. 57 and repeatedly divide by 2 noting the remainders of each division.

```

57 / 2 = 28 remainder 1 lsb

28 / 2 = 14 remainder 0

14 / 2 = 7 remainder 0

7 / 2 = 3 remainder 1

3 / 2 = 1 remainder 1

1 / 2 = 0 remainder 1 msb

```

The binary equivalent of  $57_d$  is therefore given by the remainders ordered from most significant bit (msb) to least significant bit (lsb) and is hence  $1110001_b$ .

The fractional part is given by repeatedly multiplying by 2 and storing the carries (when the result of the multiplication exceeds 1) until the required bit accuracy is reached.

```

.4801 x 2 = .9602 + 0

.9602 x 2 = .9204 + 1

.9204 x 2 = .8408 + 1

.8408 x 2 = .6816 + 1

.6816 x 2 = .3632 + 1

.3632 x 2 = .7264 + 0

.7264 x 2 = .4528 + 1

.4528 x 2 = .9056 + 0

```

and so,  $57.4801_d = 111001.01111010_b$

# OCTAL NUMBER SYSTEM

Octal number system was extensively used in earlier microcomputer system. It is also a positional weighted system having base or radix of 8. Eight symbols 0, 1, 2, 3, 4, 5, 6 and 7 are used to express octal numbers. As the base is  $8 = 2^3$ , every 3-bit

group of binary can be represented by an octal digit. Conversion between octal and binary is therefore extremely easy.

# Example-4: Convert 567.34<sub>8</sub> to equivalent binary

\_\_\_\_\_\_ 5 6 7 . 3 Octal number

3-bit binary for each octal digit 101 110 111 . 011 100 Result, putting all bits together 101110111 . 011100 $_2$

# Example-5: Convert 110101001.011101<sub>2</sub> to equivalent octal

\_\_\_\_\_\_

The binary number writing in groups of 3-bits 110 101 001 . 011 101 starting from the decimal point on either side 6 5 1 . 3 5 Octal digits, one for each group Result, putting all digits together 651 . 35<sub>8</sub>

Octal to decimal conversion can be achieved by multiplying the octal digits by their respective weights and then adding them together.

# Example-6: Convert 567.34<sub>8</sub> to equivalent decimal

```

567.34_8 = 5x8^2 + 6x8^1 + 7x8^0 + 3x8^{-1} + 4x8^{-2} = 320 + 48 + 7 + 0.375 + 0.0625 = 375.4375_{10}

```

Decimal to octal conversion for integer requires repeated division by 8 till the quotient is 0 and then putting them together from bottom to top. On the other hand, for fractions multiply the decimal fractions by 8 repeatedly till the fraction part of the product is 0 or till the required accuracy is achieved.

# Example-7: Convert 567.98<sub>10</sub> to equivalent octal number

\_\_\_\_\_\_

First let us take the integer part of the decimal number which will be successively divided by 8 to get the octal integer

567 / 8 = 70 with remainder 7lsd 70 / 8 = 08 with remainder 6 08 / 8 = 01 with remainder 001 / 8 = 00 with remainder 1 msd

The octal equivalent of the integer part of the decimal number  $567_{10}$  is given by the remainders written from msd to 1sd and is hence 10678

Now let us take the fraction part of the decimal number and multiply successively the fraction by 8 to get the octal fraction

```

.98 \times 8 = 7.84 (msd)

.84 \times 8 = 6.72

.72 \times 8 = 5.76

.76 \times 8 = 6.08

.08 \times 8 = 0.64

.64 x 8 = 5.12 and so on ......

```

Thus the fractional part of the octal number is  $0.765605_8$

So, the complete result is  $567.98_{10} = 1067.765605_{8}$

# HEXADECIMAL NUMBER SYSTEM

A useful way of expressing long pure binary coded numbers is by the use of hexadecimal numbers i.e. base 16. This is because each group of four bits (called a nibble since 2 nibbles make a byte) can be converted into one hexadecimal number. The mapping between binary, decimal and hexadecimal (hex.) numbers is shown below.

# Decimal Binary Hex Decimal Binary Hex

| 0 | 0000 | 0 | 8 | 1000 | 8 |

|---|------|---|---|------|---|

| 1 | 0001 | 1 | 9 | 1001 | 9 |

| 2 | 0010 | 2 | 10 | 1010 | Α |

|---|------|---|----|------|---|

| 3 | 0011 | 3 | 11 | 1011 | В |

| 4 | 0100 | 4 | 12 | 1100 | С |

| 5 | 0101 | 5 | 13 | 1101 | D |

| 6 | 0110 | 6 | 14 | 1110 | E |

| 7 | 0111 | 7 | 15 | 1111 | F |

To convert a binary number into its hexadecimal equivalent, first ensure that the binary number has a few bits that is a multiple of 4, if not add zeros to the left until it does. Of course, this is true in case of unsigned/positive numbers; in case of negative number, add ones to the left. Then split the number into nibbles and convert each nibble into its hexadecimal counterpart.

# Example-8: Convert the binary number 11011011011 to its hexadecimal equivalent.

The binary number 1101101101101 has 13 digits. First extend this to a multiple of 4 (i.e. 16) by adding three leading Os to the number, i.e.

11011011001101 becomes 0001101101101101

Next break the binary number up into nibbles (4-bit groups) and convert each nibble to its hexadecimal equivalent.

> 0001 1011 0110 1101 Hexadecimal 1 B 6

Hence,  $1101101101101_{b} = 1B6D_{b}$

#### SIGNED NUMBERS

In decimal system, + and - signs are used to represent positive and negative numbers. However, in binary only 0's and 1's are recognized. So a 1 or a 0 is used to represent whether a number is positive or negative. A 0 at the left indicates that the number is positive and a 1 for negative. However there are a number of ways a negative number can be represented. These are:

#### a) Sign-Magnitude (Signed Magnitude) Method:

In signed magnitude method, most significant bit (msb) is the sign bit and remaining bits are used to represent the magnitude of the number. For example, in an 8-bit binary number system,  $+/-125_{10}$  and  $+/-100_{10}$  can be represented as:

```

+125_{10} = 0111 \ 1101_2, -125_{10} = 1111 \ 1101_2

+100_{10} = 0110 \ 0100_{2}

-100_{10} = 1110 \ 0100_2

```

Arithmetic operation in signed magnitude method needs to check the signs and magnitudes of the operands before the actual operation to be performed. This increases the complexity of the circuit concerned. Also it takes more time. The complication may be avoided by representing negative numbers by their complements viz. 1's complement and 2's complement.

# b) 1's Complement Method:

In this method also the msb represents the sign of the number and remaining bits represent the magnitude. But unlike signed magnitude method, the magnitude of a negative number is represented with bit by bit complements of the corresponding positive number.  $+/-125_{10}$  and  $+/-100_{10}$  can be represented in 1's complement method as:

```

+125_{10} = 0111 \ 1101_2, -125_{10} = 1000 \ 0010_2, +100_{10} = 0110 \ 0100_2, -100_{10} = 10011011_2

```

Arithmetic operation also needs no decision making before the actual operation to be performed. But any carry generated for addition of two numbers in this method needs to be added with the result to get the correct value.

# c) 2's Complement Method:

In 2's complement method too, the msb is used to represent the sign bit and the remaining bits represent the magnitude. But the magnitude of a negative number is represented by the 2's complement of the corresponding positive number. 2's complement is calculated by adding 1 to 1's complement of the number.  $+/-125_{10}$  and  $+/-100_{10}$  can be represented in 2's complement method as:

```

+125_{10} = 0111 \ 1101_2, -125_{10} = 1000 \ 0011_2, +100_{10} = 0110 \ 0100_2, -100_{10} = 1001 \ 1100_2

```

Arithmetic operation also needs no decision making before the actual operation to be performed. Carry generated for addition of two numbers in this method is discarded.

Example-9: Represent the following decimal numbers in 8-bit singed magnitude, 1's and 2's complement forms:  $+35_d$ ,  $-35_d$ ,  $+65_d$ ,  $-65_d$ ,  $+127_d$ ,  $-127_d$ ,  $+128_d$ ,  $-128_d$

\_\_\_\_\_\_

| Decimal | 3                   |                |                |                   |

|---------|---------------------|----------------|----------------|-------------------|

| Number  | Signed<br>Magnitude | 1's Complement | 2's Complement | Remarks           |

| +35     | 0 001 0011          | 0 001 0011     | 0 001 0011     | 2's complement    |

| -35     | 1 001 0011          | 1 110 1100     | 1 110 1101     | representation    |

| +65     | 0 010 0001          | 0 010 0001     | 0 010 0001     | has only one 0    |

| -65     | 1 010 0001          | 1 101 1110     | 1 101 1111     | unlike signed     |

| +127    | 0 111 1111          | 0 111 1111     | 0 111 1111     | magnitude and 1's |

| -127    | 1 111 1111          | 1 000 0000     | 1 000 0001     | complement system |

| +128 | Out of range. Range is: -127 to -0, +0 to | Out of range. Range is: -127 to -0, +0 to | Out of range. Range is: -128 to -1, 0, +1 to +127 | which have two 0s |

|------|-------------------------------------------|-------------------------------------------|---------------------------------------------------|-------------------|

| -128 | +127                                      | +127                                      | 1000 0000                                         | namely -0 and +0  |

# Shortcut methods of finding 2's complements are as follows:

Method-2: -128 in 2's complement is 1000 0000 and thus the sign bit (msb) can be considered to have a positional weight of -128 and other places have their usual weights but positive i.e. the weights of the bits of an 8-bit 2's complement representation are -128, +64, +32, +16, +8, +4, +2, +1. So any -ve number can be expressed as sum of -128 and some positive values in 2's powers and then can be represented by putting 1s in their respective positions.

```

Example-10: Represent, -128, -127, -80, -10 and -1 in 2's complement system

```

\_\_\_\_\_\_

```

a) -128_d = -128+0

= 1000 0000_{2}

b) -127_d = -128+1

= 1000 0001_2

c) -80_d = -128 + 32 + 16

= 1011 0000_2

d) -10_d = -128+64+32+16+4+2 = \frac{1}{1}111 01110_2

e) -1_d = -128+64+32+16+8+4+2+1 = 1111 1111_2

```

Method-3: First represent the positive number in equivalent binary; proceed from the right (lsb), keep the bits unchanged up to and including the first 1 and then complement all the remaining bits.

Example-11: Express the numbers of Example-10 in 2's complement following the third method.

| -ve Number        | Corresponding +ve number | Binary representation | -ve number in 2's      |

|-------------------|--------------------------|-----------------------|------------------------|

|                   |                          | of +128               | complement form        |

| -128 <sub>D</sub> | 128 <sub>D</sub>         | 1000 0000             | 1000 00002             |

| -127 <sub>D</sub> | 127 <sub>D</sub>         | 0111 1111             | 1000 00012             |

| -80 <sub>D</sub>  | 80 <sub>D</sub>          | 0101 0000             | 1011 0000 <sub>2</sub> |

| -10 <sub>D</sub>  | 10 <sub>D</sub>          | 0000 1010             | 1111 01102             |

| -1 <sub>D</sub>   | 1 <sub>D</sub>           | 0000 0001             | 1111 1111 <sub>2</sub> |

#### BINARY ARITHMETIC

## Signed Magnitude Arithmetic

Binary addition and subtraction in signed magnitude method require certain decision before and after the actual operation is performed. Let us take the following examples:

| + 98 | +98 | -98 | - 98 |

|------|-----|-----|------|

| + 78 | -78 | +78 | - 78 |

|      |     |     |      |

| +176 | +20 | -20 | -176 |

The observations are:

- a) If signs of both the operands are identical, they will be added and the sign of the result will be that of either of them.

- b) If their signs are different, the smaller operand will be subtracted from the larger one and the sign of the result will be that of the larger operand.

Implementation of signed magnitude arithmetic requires more hardware. Decision making also takes larger time to complete the operation and thus is not followed in computer system. Rather subtraction in computer system is implemented through addition; the complement of the subtrahend is added with the minuend.

## 1's Complement Arithmetic

- a) Express the subtrahend in 1's complement form

- b) Add it with the minuend

- c) If there is a carry out, bring the carry around and add it to the lsb. This is called the *end around carry*.

- d) If the sign bit (msb) is 0, the result is +ve

- e) If it is 1, the result is -ve and is in 1's complement form. Take its 1's complement to get the magnitude of the result.

Example-12: Perform using 8-bit 1's complement method: a) 127 - 59, b) 59 - 127, c) -35 - 65 and d) 35 + 65

a) 127 **0**111 1111

```

-59 +1100 0100 1's complement of 59

+68 10100 0011

> +1

-------

0100 0100

1's complement of 59

End around carry to be added with 1sb

```

The msb is 0, the result is +ve and is in pure binary. Therefore, the result is  $+68_{\rm d}$ .

The msb is 1, the result is -ve and is in 1's complement form. 1's complement of  $1011\ 1011\ is 0100\ 0100$ . Therefore, the result is -68.

The msb is 1, the result is -ve and is in 1's complement form. 1's complement of 1001 1011 is 0110 0100. Therefore, the result is -100.

```

35

0010 0011

d)

+0100 0001

+65

+100 0110 0100

```

The msb is 0, the result is +ve and is in pure binary. Therefore, the result is  $+100_{d}$ .

#### 2's Complement Arithmetic

- a) Express the subtrahend in 2's complement form

- b) Add it with the minuend

- c) Ignore carry out, if any

- d) If the sign bit (msb) is 0, the result is +ve

- e) If it is 1, the result is -ve and is in 2's complement form. Take its 2's complement to get the magnitude of the result.

Example-13: Perform using 8-bit 2's complement method: a) 127 - 59, b) 59 - 127, c) -35 - 65 and d) 35 + 65

\_\_\_\_\_\_

```

127 0111 1111

a)

-59 +1100 0101 2's complement of 59

_____

+ 68

10100 0100

0100 0100 Final result ignoring carry

```

The msb is 0, the result is +ve and is in pure binary. Therefore, the result is +68<sub>d</sub>.

```

b)

59

0011 1011

-127 +1000 0001 2's complement of 127

- 68 1011 1100

```

The msb is 1, the result is -ve and is in 2's complement form. 2's complement of 1011 1100 is 0100 0100. Therefore, the result is -68.

```

-35

1101 1101 2's complement of 35

C)

-65 +1011 1111 2's complement of 65

-----

-100 1<u>1</u>001 1100

1001 1100 Final result ignoring carry

```

The msb is 1, the result is -veand is in 2's complement form. 2's complement of 1001 1100 is 0110 0100. Therefore, the result is -100.

```

35

d)

0010 0011

+65 +0100 0001

+100 0110 0100

```

The msb is 0, the result is +ve and is in pure binary. Therefore, the result is  $+100_{d}$ .

| 30.125  | 0001 1110.0010       |                                                    |

|---------|----------------------|----------------------------------------------------|

| -93.625 | + <mark>1</mark> 010 | 2's complement of 93.625 (express 93.625 in binary |

|         | 0010.0110            | and then take 2's complement of the whole number   |

|         |                      | ignoring the decimal point)                        |

| -63.500 | 1100 0000.1000       | No carry                                           |

The msb is 1, the result is -ve and is in 2's complement form. 2's complement of  $1100\ 0000.1000$  is  $0011\ 1111.1000$ . Therefore, the result is -63.5.

Example-15: Considering 8-bit 2's complement system, add (i) -100 -30, (ii) 100 +30 and explain the overflow condition

\_\_\_\_\_\_

$30d = 0001 \ 1110_b \ -30d = 1110 \ 0010_b \ 100d = 0110 \ 0100_b \ -100d = 1001 \ 1100_b$

-130 is out of the range as in 8-bit 2's complement system the range of number is: -128 to +127. This is an overflow condition and is satisfied by the carry flow (no carry from D6 but a carry from D7).

+130 is again out of the range. This is an overflow condition and is satisfied by the carry flow (a carry from D6 but no carry from D7).

# Note:

- 1. In case of -ve mixed number (integer plus fraction), if you observe carefully the integer part in 2's complement form, you will find that it is actually the 2's complement of the next higher number. For example, 1010 0010 is 2's complement of 94 (not of 93) i.e. -94. Therefore, the fraction should be positive and it must be +0.375 so that -94 + 0.375 will be producing -93.625. So in complement representation, fraction is always considered to be positive.

- 2. In case of signed arithmetic, if the result is not limited within the range of the numbers of the system, overflow occurs. Consider two numbers a and b. If we subtract a from b, the result can't have a greater magnitude than either a or b. Therefore, adding two numbers of different sign cannot generate overflow. If a and b have the same sign, but a+b has a different sign, then overflow has occurred.

- 3. Also overflow is said to occur if there is a carry either from D6 or from D7 position but not from the both.

# Binary Codes

Representation of Numerals and Alphabets plus Numerals in terms of binary numbers is called Binary Coding. The binary number itself is called the binary code. The binary codes representing numerals are called Numeric codes and that representing Alphanumeric information are called Alphanumeric Codes.

### Binary Codes

- 1. Numeric: Numeric Codes may also be classified as Weighted, Non-weighted, Self Complementing, Sequential, Error Detecting and Correcting, Reflective and Cyclic

- o Weighted: In weighted code, each binary bit position is having a fixed value called weight. Examples are Binary and BCD codes. BCD codes may also be classified as positively weighted and negatively weighted. In positively weighted codes, all the positional weights are positive and for negatively weighted codes, some of the positional weights are negative. Examples of positively weighted codes are: 8421, 4221, 2421, 5211, 3321 and 4311 are some of 17 such codes. Examples of negatively weighted codes: 642-3, 631-1, 84-2-1 etc. All these are BCD codes.

- o Non-weighted: In non-weighted code, the bits are having no fixed values or weights. Examples are: Gray, Excess-3 etc. Non-weighted codes are not suitable for arithmetic operations.

- o Self Complementing: 9's complement can be calculated by interchanging 0's and 1's in the code. 2421, 5211 and XS-3 are examples of self-complementing codes.

- o Sequential: The codes in which succeeding code word is one greater than the preceding one. 8421, XS-3 are sequential codes.

- o Error Detecting and Correcting: Data transmission from one place to other distant place or even within a computer, 1 or 0 may be misinterpreted as 0 or 1due to noise. Error detection techniques allow detecting such errors, while error correction enables reconstruction of the original data in many cases. Parity and Hamming codes are used to detect and correct errors respectively.

- o Reflective: It is a binary code where two successive values differ by one bit only. The name "reflective" was coined by Bell Labs researcher Frank Grey since it may be built up from the conventional binary code by a sort of reflection process. The code later became popular after the name of Gray. The reflected binary code was originally designed to prevent spurious output from electromechanical switches. Today, Gray codes are widely used to facilitate error correction in digital communications such as digital terrestrial television and some cable TV systems.

| Doo | Cmarr | Dinom  |

|-----|-------|--------|

| Dec | Gray  | Binary |

| 0   | 000   | 000    |

| 1   | 001   | 001    |

| 2   | 011   | 010    |

| 3   | 010   | 011    |

| 4   | 110   | 100    |

| 5   | 111   | 101    |

| 6   | 101   | 110    |

| 7   | 100   | 111    |

- o Cyclic: The code in which each code word differs from the preceding code word in only one bit position is called cyclic code. Gray code is a cyclic code. Sometimes it is also called unit distant code.

- 2. Alphanumeric: Computers not only need to process numeric data, also they have to process letters of alphabet, special characters and symbols. Binary codes representing alphabet, numerals, special characters, and symbols are called Alphanumeric codes. Examples are ASCII, EBCDIC, Hollerith. Input output devices such as keyboards, monitors, mouse can be interfaced using these codes.

The full form of **ASCII code** is American Standard Code for Information Interchange. It is a seven-bit code based on the English alphabet. In 1967 this code was first published and since then it is being modified and updated. ASCII code has 128 characters.

The EBCDIC stands for Extended Binary Coded Decimal Interchange Code. IBM

invented this code to extend the Binary Coded Decimal which existed at that time. All the IBM computers and peripherals use this code. It is an 8-bit code and therefore can accommodate 256 characters.

Hollerith code is a code for relating alphanumeric characters to holes in a punched card. It was devised by Herman Hollerith in 1888 and enabled the letters of the alphabet and the digits 0-9 to be encoded by a combination of punchings in 12 rows of a card.

The usual way of expressing a decimal number in terms of a binary number is known as pure binary coding. A number of other techniques can be used to represent a decimal number. These are:

#### 8421 BCD Code

In the 8421 Binary Coded Decimal (BCD) representation each decimal digit is converted to its 4-bit pure binary equivalent.

For example: 57 dec = 0101 0111bcd

Addition is analogous to decimal addition with normal binary addition taking place from right to left. For example,

| 6  | 0110 | BCD | for | 6 | 42  | 0100 | 0010 | BCD | for | 42 |

|----|------|-----|-----|---|-----|------|------|-----|-----|----|

| +3 | 0011 | BCD | for | 3 | +27 | 0010 | 0111 | BCD | for | 27 |

|    | 1001 | BCD | for | 9 |     | 0110 | 1001 | BCD | for | 69 |

Where the result of any addition exceeds 9(1001) then six (0110) must be added to the sum to account for the six invalid BCD codes that are available with a 4-bit number. Six (0110) must also be added to the sum in case there is a carry. This is illustrated in the examples below:

| 8    | 1000 | BCD for | 8            |

|------|------|---------|--------------|

| +7   | 0111 | BCD for | 7            |

|      | 1111 | exceeds | 9 (1001), so |

|      |      | add six |              |

| 0001 |      | BCD for |              |

|      |      |         |              |

| 9    | 1001 | BCD for | 9            |

| +9   | 1001 | BCD for | 9            |

| 1    | 0010 | A carry | is generated |

|      | 0110 | Add six | (0110)       |

| 0001 | 1000 | BCD for | 18           |

Note that in the last examples the 1 that carried forward from the first group of 4 bits has made a new 4-bit number and so represents the "1" in "15" or "18". In the examples above the BCD numbers are split at every 4-bit boundary to make reading them easier. This is not necessary when writing down a BCD number.

#### 4221 BCD Code

The 4221 BCD code is another binary coded decimal code where each bit is weighted by 4, 2, 2 and 1 respectively. Unlike BCD coding there are no invalid representations. The decimal numbers 0 to 9 have the following 4221 equivalents

| Decimal | 4221 | 1's complement |

|---------|------|----------------|

| 0       | 0000 | 1111           |

| 1       | 0001 | 1110           |

| 2       | 0010 | 1101           |

| 3       | 0011 | 1100           |

| 4       | 1000 | 0111           |

| 5       | 0111 | 1000           |

| 6       | 1100 | 0011           |

| 7       | 1101 | 0010           |

| 8       | 1110 | 0001           |

| 9       | 1111 | 0000           |

The 1's complement of a 4221 representation is important in decimal arithmetic. In forming the code remember the following rules

- Below decimal 5, use the right-most bit representing 2 first

- Above decimal 5, use the left-most bit representing 2 first

- Decimal 5 = 2+2+1 and not 4+1

#### Gray Code

Gray coding is an important code and is used for its speed, it is also relatively free from errors. In pure binary coding or 8421 BCD, the counting from 7 (0111) to 8 (1000) requires 4 bits to be changed simultaneously. If this does not happen at a time then various numbers could be momentarily generated during the transition so creating spurious numbers which could be read.

Gray coding avoids this since only one bit changes between subsequent numbers. To construct the code there are two simple rules. First start with all 0s and then proceed by changing the least significant bit (lsb) which will bring about a new

The first 16 Gray coded numbers are indicated below.

| Decimal | Binary | Gray Code | Decimal | Binary | Gray Code |

|---------|--------|-----------|---------|--------|-----------|

| 0       | 0000   | 0000      | 8       | 1000   | 1100      |

| 1       | 0001   | 0001      | 9       | 1001   | 1101      |

| 2       | 0010   | 0011      | 10      | 1010   | 1111      |

| 3       | 0011   | 0010      | 11      | 1011   | 1110      |

| 4       | 0100   | 0110      | 12      | 1100   | 1010      |

| 5       | 0101   | 0111      | 13      | 1101   | 1011      |

| 6       | 0110   | 0101      | 14      | 1110   | 1001      |

| 7       | 0111   | 0100      | 15      | 1111   | 1000      |

# Code Conversion: Binary to Gray

```

G_n = B_n

G_{n-1} = B_n XOR B_{n-1}

G_{n-2} = B_{n-1} XOR B_{n-2}

G_1 = B_2 \text{ XOR } B_1

```

The conversion procedure is as follows:

- Record the MSB of Binary as MSB of Gray

- Add the MSB of the binary to the next bit of the binary, recording the sum and ignoring the carry, if any, i.e. XOR the bits. This sum is the next bit of the Gray code.

- Add the second bit of the binary to the 3rd bit of Binary, 3rd bit to the 4th bit, and so on.

- Record the successive sums as the successive bits of gray code until all the bits of binary are exhausted.

Example-16: Convert the binary 1010 to Gray code.

| Binary         | 1 | 0 | 1 | 0 |                                   |

|----------------|---|---|---|---|-----------------------------------|

| Shifted binary |   | 1 | 0 | 1 | 0                                 |

|                |   |   |   |   |                                   |

| Gray           | 1 | 1 | 1 | 1 | (Taking Sum and discarding Carry) |

# Gray to Binary:

```

B_n = G_n

B_{n-1} = B_n \text{ XOR } G_{n-1}

B_{n-2} = B_{n-1} \text{ XOR } G_{n-2}

B_1 = B_2 \text{ XOR } G_1

```

Conversion Procedure:

- Record the MSB of Gray as MSB of Binary

- Add the MSB of the binary to the next significant bit of Gray i.e. XOR the bits. Record the sum and ignore the carry.

- Add the second bit of the binary to the 3rd bit of Gray, 3rd bit to the 4th bit of the Gray, and so on.

- · Continue this till all the Gray bits are exhausted. The sequence of bits that has been written down is the binary equivalent of the Gray code number.

Example-17: Covert the Gray code 1111 to binary.

Gray Binary

Example-18: Convert the Gray coded number 10011011 to its binary equivalent.

```

______

B_7 = G_7

B_6 = B_7 \text{ XOR } G_6 = 1 \text{ XOR } 0 = 1

B_5 = B_6 \text{ XOR } G_5 = 1 \text{ XOR } 0 = 1

B_4 = B_5 \text{ XOR } G_4 = 1 \text{ XOR } 1 = 0

B_3 = B_4 \text{ XOR } G_3 = 0 \text{ XOR } 1 = 1

B_2 = B_3 \text{ XOR } G_2 = 1 \text{ XOR } 0 = 1

B_1 = B_2 \text{ XOR } G_1 = 1 \text{ XOR } 1 = 0

B_0 = B_1 \text{ XOR } G_0 = 0 \text{ XOR } 1 = 1

```

So, 10011011 gray = 11101101 bin

Gray coding is a non-BCD, non-weighted reflected binary code.

#### FURTHER READING ON CODING:

#### ASCII Code

The American Standard Code for Information Interchange (ASCII) is a characterencoding scheme originally based on the English alphabet that encodes 128 specified characters – the numbers 0-9, the letters a-z and A-Z, some basic punctuation symbols, some control codes that originated with Teletype machines, and a blank space - into the 7-bit binary integers.

ASCII codes represent text in computers, communications equipment, and other devices that use text. Most modern character-encoding schemes are based on ASCII, though they support many additional characters. The ASCII Table is given below.

| ASCII Hex Symbol                                                                                                                                  | ASCII Hex Symbol                                                                                                                                           | ASCII Hex Symbol                                                                                                                            | ASCII Hex Symbol                                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0 NUL 1 1 SOH 2 2 STX 3 3 ETX 4 4 EOT 5 5 ENQ 6 6 ACK 7 7 BEL 8 8 BS 9 9 TAB 10 A LF 11 B VT 12 C FF 13 D CR 14 E SO 15 F SI                    | 16 10 DLE 17 11 DC1 18 12 DC2 19 13 DC3 20 14 DC4 21 15 NAK 22 16 SYN 23 17 ETB 24 18 CAN 25 19 EM 26 1A SUB 27 1B ESC 28 1C FS 29 1D GS 30 1E RS 31 1F US | 32 20 (space) 33 21 ! 34 22 " 35 23 # 36 24 \$ 37 25 % 38 26 & 39 27 ' 40 28 ( 41 29 ) 42 2A * 43 2B + 44 2C , 45 2D - 46 2E . 47 2F /      | 48 30 0<br>49 31 1<br>50 32 2<br>51 33 3<br>52 34 4<br>53 35 5<br>54 36 6<br>55 37 7<br>56 38 8<br>57 39 9<br>58 3A :<br>59 3B ;<br>60 3C <<br>61 3D =<br>62 3E ><br>63 3F ? |

| ASCII Hex Symbol  64 40 @ 65 41 A 66 42 B 67 43 C 68 44 D 69 45 E 70 46 F 71 47 G 72 48 H 73 49 I 74 4A J 75 4B K 76 4C L 77 4D M 78 4E N 79 4F O | 80 50 P 81 51 Q 82 52 R 83 53 S 84 54 T 85 55 U 86 56 V 87 57 W 88 58 X 89 59 Y 90 5A Z 91 5B [ 92 5C \ 93 5D ] 94 5E 95 5F                                | 96 60 \ 97 61 a 98 62 b 99 63 c 100 64 d 101 65 e 102 66 f 103 67 g 104 68 h 105 69 i 106 6A j 107 6B k 108 6C 1 109 6D m 110 6E n 111 6F o | ASCII Hex Symbol  112 70 113 71                                                                                                                                              |

# EBCDIC Codes

Extended Binary Coded Decimal Interchange Code (EBCDIC) is an 8-bit character encoding used mainly on IBM mainframe and IBM midrange computer operating systems.

| Dec Hx Oct Char                              | 1                                              | Dec        | Нх       | Oct        | Char | Dec        | Hx | Oct        | Char   | Dec Hx           | Oct        | Char   |

|----------------------------------------------|------------------------------------------------|------------|----------|------------|------|------------|----|------------|--------|------------------|------------|--------|

| 0 0 000 <b>nul</b> (Null                     | 1)                                             | 65         | 41       | 101        |      | 130        | 82 | 202        | b      | 195 c3           | 303        | С      |

|                                              | art of Heading)                                | 66         | 42       | 102        |      | 131        | 83 | 203        | С      | 196 c4           | 304        | D      |

|                                              | art of Text)                                   | 67         |          | 103        |      | 132        |    | 204        | d      | 197 c5           | 305        | Е      |

|                                              | d of Text)                                     | 68         |          | 104        |      | 133        |    | 205        | e      | 198 c6           | 306        | F      |

|                                              | nch Off)                                       | 69         |          | 105        |      | 134        |    | 206        | f      | 199 c7           | 307        | G      |

| 5 5 005 ht (Hor                              | rizontal Tab)                                  | 70         | 46       |            |      | 135        |    |            | g      | 200 c8           | 310        | H      |

|                                              | wer Case)                                      | 71         |          | 107        |      | 136        |    | 210        | h i    | 201 c9           | 311        |        |

| 7 7 007 del (Del<br>8 8 010 ge               | lete)                                          | 72<br>73   |          | 110<br>111 |      | 137<br>138 |    | 211<br>212 | i      | 202 ca<br>203 cb | 312        |        |

| 8 8 010 ge<br>9 9 011 rlf                    |                                                | 74         |          | 112        | d    | 139        |    | 213        |        | 203 CB           | 314        |        |

|                                              | art of Manual Message)                         | 75         |          | 113        | Ψ    | 140        |    | 214        |        | 205 cd           | 315        |        |

|                                              | rtical Tab)                                    | 76         |          | 114        | × ×  | 141        |    | 215        |        | 206 ce           | 316        |        |

|                                              | m Feed)                                        | 77         |          | 115        |      | 142        |    | 216        |        | 207 cf           | 317        |        |

|                                              | rriage Réturn)                                 | 78         |          | 116        |      | 143        | 8f | 217        |        | 208 d0           | 320        | }      |

| 14 e 016 <mark>so</mark> (Shi                | ift Out)                                       | 79         | 4f       | 117        | 1    | 144        | 90 | 220        |        | 209 d1           | 321        | Ĵ      |

|                                              | ift in)                                        | 80         |          | 120        | &    | 145        |    | 221        | j      | 210 d2           | 322        | K      |

|                                              | ta Link Escape)                                | 81         |          | 121        |      | 146        |    | 222        | k      | 211 d3           | 323        | L      |

|                                              | vice Control 1)                                | 82         | 52       |            |      | 147        |    | 223        |        | 212 d4           | 324        | M      |

|                                              | (Device Control 2)                             | 83         | 53       |            |      | 148        |    | 224        | m      | 213 d5           | 325        | N      |

|                                              | oe Mark)<br>store)                             | 84<br>85   | 54<br>55 |            |      | 149<br>150 |    | 225<br>226 | n<br>o | 214 d6<br>215 d7 | 326<br>327 | P      |

|                                              | w Line)                                        | 86         | 56       |            |      | 151        |    | 227        | р      | 216 d8           | 330        | á      |

|                                              | ckspace)                                       | 87         |          | 127        |      | 152        |    | 230        | q      | 217 d9           | 331        | Ř      |

| 23 17 027 il (Idle                           |                                                | 88         |          | 130        |      | 153        |    | 231        | ř      | 218 da           | 332        |        |

| 24 18 030 can (Car                           | ncel)                                          | 89         | 59       | 131        |      | 154        | 9a | 232        |        | 219 db           | 333        |        |

| 25 19 031 em (End                            | d of Medium)                                   | 90         | 5a       | 132        | Į.   | 155        | 9b | 233        |        | 220 dc           | 334        |        |

|                                              | rsor Control)                                  | 91         |          | 133        |      | 156        |    | 234        |        | 221 dd           | 335        |        |

|                                              | stomer Use 1)                                  |            |          | 134        |      | 157        |    | 235        |        | 222 de           | 336        |        |

|                                              | erchange File Separator)                       | 93         |          | 135        |      | 158        |    | 236        |        | 223 df           | 337        |        |

|                                              | erchange Group Separator)  <br>erchange Record | 94<br>95   |          | 136<br>137 | i e  | 159<br>160 |    | 237        |        | 224 e0<br>225 e1 | 340<br>341 | A.     |

|                                              | erchange Necord<br>erchange Unit Separator)    | 96         | 60       |            | _    | 161        |    | 241        |        | 225 e1<br>226 e2 | 342        | s      |

|                                              | it Select)                                     | 97         | 61       |            | 1    | 162        |    | 242        | s      | 227 e3           | 343        | Ť      |

|                                              | art of Significance)                           | 98         | 62       |            |      | 163        |    | 243        | t      | 228 e4           | 344        | Ù      |

| 34 22 042 fs (Fiel                           | ld Separator)                                  | 99         | 63       | 143        |      | 164        | a4 | 244        | u      | 229 e5           | 345        | V      |

| 35 23 043                                    |                                                | 100        | 64       |            |      | 165        | a5 | 245        | ٧      | 230 e6           | 346        | W      |

|                                              | pass) _                                        | 101        | 65       |            |      | 166        |    | 246        | W      | 231 e7           | 347        | X      |

|                                              | e Feed)                                        | 102        | 66       |            |      | 167        |    | 247        | ×      | 232 e8           | 350        | Y      |

|                                              | d of Transmission Block)                       | 103<br>104 | 67<br>68 |            |      | 168<br>169 |    | 250<br>251 | y .    | 233 e9<br>234 ea | 351<br>352 | Z      |

| 40 28 050                                    | cape)                                          | 105        | 69       |            |      | 170        |    | 252        | Z      | 235 eb           | 353        |        |

| 41 29 051                                    |                                                | 106        | 6a       |            | 1    | 171        |    | 253        |        | 236 ec           | 354        |        |

|                                              | t Mode)                                        | 107        | 6b       |            | - 1  | 172        |    | 254        |        | 237 ed           | 355        |        |

| ,                                            | stomer Use 2)                                  | 108        | 6c       |            | %    | 173        |    | 255        |        | 238 ee           | 356        |        |

| 44 2c 054                                    | , i                                            | 109        | 6d       | 155        |      | 174        | ae | 256        |        | 239 eF           | 357        |        |

|                                              | quiry)                                         | 110        | 6e       |            | <    | 175        |    | 257        |        | 240 f0           | 360        | 0      |

|                                              | knowledge)                                     | 111        |          | 157        | ?    | 176        |    | 260        |        | 241 f1           | 361        | 1      |

| 47 2f 057 bel (Bell                          | I)                                             | 112        |          |            |      | 177        |    | 261        |        | 242 f2           | 362        | 2      |

| 48 30 060<br>49 31 061                       |                                                | 113<br>114 |          | 161<br>162 |      | 178<br>179 |    | 262<br>263 |        | 243 f3<br>244 f4 | 363<br>364 | 3<br>4 |

|                                              | nchronous Idle)                                |            |          | 163        |      | 180        |    | 264        |        | 245 f5           | 365        | 5      |

| 51 33 063                                    | nerii orious iule)                             | 116        |          |            |      | 181        |    | 265        |        | 246 f6           | 366        | 6      |

|                                              | nch On)                                        |            | 75       |            |      | 182        |    | 266        |        | 247 f7           | 367        | 7      |

|                                              | ader Stop)                                     | 118        |          |            |      | 183        |    | 267        |        | 248 f8           | 370        | 8      |

| 54 36 066 uc (Up;                            | per Case)                                      | 119        | 77       | 167        |      | 184        |    | 270        |        | 249 f9           | 371        | 9      |

|                                              | d of Transmission)                             | 120        |          |            |      | 185        |    | 271        |        | 250 fa           | 372        |        |

| 56 38 070                                    |                                                | 121        | 79       |            |      | 186        |    | 272        |        | 251 fb           | 373        |        |

| 57 39 071<br>59 35 073                       |                                                | 122        |          |            | :    | 187        |    | 273        |        | 252 fc           | 374        |        |

| 58 3a 072<br>59 3b 073 <mark>cu3</mark> (Cus | stomer Use 3)                                  | 123        |          |            | #    | 188        |    | 274        |        | 253 fd           | 375        |        |

|                                              | vice Control 4)                                | 124<br>125 | 70<br>7d |            | @    | 189<br>190 |    | 275<br>276 |        | 254 fe<br>255 ff | 376<br>377 | eo     |

|                                              | gative Acknowledge)                            |            | 7e       |            | _    | 191        |    | 277        |        | 200 11           | 511        | 00     |

| 62 3e 076                                    | gerionierioago)                                | 127        |          | 177        |      | 192        |    | 300        | {      |                  |            |        |

| 63 3f 077 sub (Suk                           | bstitute)                                      | 128        | 80       | 200        |      | 193        | c1 | 301        | À      |                  |            |        |

|                                              | ace)                                           | 129        |          | 201        | а    | 194        | c2 | 302        | В      |                  |            |        |

|                                              | ·                                              |            |          |            |      | -          | _  |            |        |                  |            |        |

Source: www.pubblinet.com

# Additional Reading:

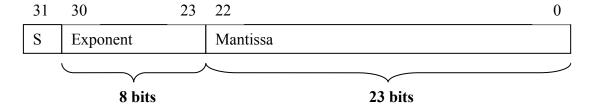

#### Floating Point data:

- It is similar to scientific notation in base 10

- The floating point format is suitable to express large numbers

- It is used to store mixed as well as integer data

- Floating point numbers are often stored in four bytes

- Format of 4-byte (single precision) floating point number is:

- The left most bit indicates the sign of the mantissa

- Next 8 bits are for exponent stored in excess 127 notation

- Exponent in excess 127 is an unsigned integer that is equal to the actual exponent plus 127

- Mantissa is a normalized 23-bit number with a hidden or implied 1 in 24th bit position

### Examples:

100 - 1100100 - 1 1001 - 26

$100_{10} = 1100100_2 = 1.1001 \times 2^6$

S Exponent Mantissa

$-12.7010 = -1100.112 = 1.10011 \times 23$

S Exponent Mantissa

The term floating point is derived from the fact that there is no fixed number of digits before and after the decimal point; that is, the decimal point can float. There are also representations in which the number of digits before and after the decimal point is set, called fixed-point representations. In general, floating-point representations are slower and less accurate than fixed-point representations, but they can handle a larger range of numbers.

Note that most floating-point numbers a computer can represent are just approximations. One of the challenges in programming with floating-point values is ensuring that the approximations lead to reasonable results. If the programmer is not careful, small discrepancies in the approximations can snowball to the point where the final results become meaningless.

Because mathematics with floating-point numbers requires a great deal of computing power, many microprocessors come with a Chip, called a floating point unit (FPU), specialized for performing floating-point arithmetic. FPUs are also called math coprocessors and numeric coprocessors.

# College of Engineering & Management, Kolaghat

# Sample Questions and answers

- 1. Convert the following numbers in 8-bit binary codes:

- (a)  $127_{10}$ , (b)  $63_8$ , (c)  $85.95_{10}$  (up to 4 bit fraction).

- a)  $127_{10} = 64+32+16+8+4+2+1 = 0111 1111_2$

- b)  $63_8 = 110 \ 011_2$  (just converting each octal digit to its equivalent binary code).

- c)  $85.95_{10} = (64+16+4+1)+(0.5+0.25+0.125+0.0625) = 0101 0101.1111$

- 2. Express the following Decimal Numbers in 8-bit Binary code:

- -120 in signed magnitude, (b) -108 in 1's complement, (c) -125 - in 2's complement.

- a)  $-120_{10} = -(64+32+16+8) = 1111 \ 1000_2 in signed magnitude$

- b)  $-108_{10} = 1$ 's complement of +108 (0110 1100) = 1001 0011

- c)  $-125_{10} = 2$ 's complement of +125 (0111 1101) = 1000 0011

- 3. Express the following decimal number in BCD codes:

- (a) 79, (b) 65, (c) 63; a) & b) in 8421 BCD and c) in 4221 BCD codes

- a)  $79_{10} = 0111 \ 1001 in \ 8421 \ BCD$

- b)  $65_{10} = 0110 \ 0101 in 8421 \ BCD$

- c)  $63_{10} = 1100 \ 0011 in \ 4221 \ BCD$

- 4 . Express the following signed binary numbers (2's complement) to equivalent Decimal Numbers:

- (a) 1011 1111, (b) 1010 1010, (c) 0111 1111

- a) 1011 1111, its msb being 1, it is -ve and its magnitude can be found by taking its 2's complement. 1011 1111 => 2's complement is 0100 0001 => 65. So the number is  $-65_{10}$

- b) 1010 1010, msb being 1, it is -ve and its magnitude can be found by taking its 2's complement. 1010 1010  $\Rightarrow$  2's complement is 0101  $0110 = > -86_{10}$

- c) 0111 1111, msb being 0, it is +ve and its magnitude is 127. So the number is  $+127_{10}$ .

- 5. Convert the following numbers into Gray Codes:

110111

- (a)  $45_8$ , (b)  $97_{10}$ , (c)  $1010 \ 1010_2$

- a)  $45_8 = 100 \ 101_2$

Gray Code

100101 Binary Shifted Binary 100101 \_\_\_\_\_  $b) 97_{10} = 110 0001_2$

c) Binary 10101010 Shifted Binary 10101010

\_\_\_\_\_

Gray 11111111

# 6. Do the following operations:

(a) (-100-15) in 1's complement method

-100 = 1's complement of +100

$+100 = 0110 \ 0100$

$-100 = 1001 \ 1011$

+15 = 0000 1111

$-15 = 1111 \ 0000$

$-100 = 1001 \ 1011$

-15 = 1111 0000

\_\_\_\_\_

-115 = 1 1000 1011

adding end around carry  $\Rightarrow$  1000 1100, msb being 1, answer is -ve and the magnitude can be obtained by taking 1's complement which gives, 0111 0011  $\Rightarrow$  115. So the result is -115 which matches with the decimal addition.

(b) (-128+127) in 2's complement method

-128 = 1000 0000

+127 = 0111 1111

\_\_\_\_\_

-1 = 1111 1111, msb being 1, answer is -ve and the magnitude can be obtained by taking 2's complement which gives, 0000 0001 => 1. So the result is -1 which matches with the decimal addition.

# Boolean Algebra:

Various Logic Gates - their truth tables and circuits

#### INTRODUCTION

We have learned that binary variables can assume only two values, and these are called logic values; logic 1 and logic 0. They may also be denoted as ON/OFF, HIGH/LOW, YES/NO, TRUE/FALSE. Logical operators operate on binary values and binary variables. Variable identifiers may be A, B, C, x, y, z, RESET, START etc.

Basic **logical operators** are logic functions OR, AND and NOT. Logic gates are electronic circuits implementing logic functions. Mathematical system developed for specifying and transforming logic functions is called **Boolean Algebra**. We study Boolean algebra as a foundation for designing and analyzing digital systems.

**AND** is denoted as a dot (.), OR is denoted by a plus (+) and NOT is denoted by an over bar  $(\bar{\ })$ , a single quote mark (') after, or  $(\sim)$  before the variable. For Example Y = A.B is read as "Y is equal to A AND B"

z = x + y is read as "z is equal to x OR y" and

$X = {}^{\sim}A$  is read as "X is equal to NOT A"

Behaviors of logic functions can be defined in words or in a table. Such a table lists all possible combinations of input variables and corresponding outputs and is called a *truth table*.

#### AND GATE

An AND gate has two or more inputs and only one output. The output assumes logic 1 when all the inputs assume logic 1 and assumes logic 0 when any one of its inputs assumes logic 1. Therefore, the AND gate may be defined as a device whose output is 1 if and only if all its inputs are 1. Thus, an AND gate is also called all or nothing gate. The logic symbol and the truth table for a two-input AND gate is shown in Fig.1.

| Inp | Output |       |

|-----|--------|-------|

| А   | В      | Y=A.B |

| 0   | 0      | 0     |

| 0   | 1      | 0     |

| 1   | 0      | 0     |

| 1   | 1      | 1     |

Logic symbol

(b) Truth Table

Fig.1: A two-input AND Gate

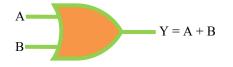

#### OR GATE

Like an AND gate, an OR gate may also have two or more inputs and only one output. The output assumes logic 1 when any of its inputs assumes logic 1 and assumes logic 0 when all the inputs assume logic 0. Therefore, an OR may be defined as a device whose output is 1, even if one of its inputs is 1. Hence an OR gate is called any or all gates. The logic symbol and the truth table of a two-input OR gate is shown in Fig.2.

| 1110 | uls | Output |

|------|-----|--------|

| А    | В   | Y=A+B  |

| 0    | 0   | 0      |

| 0    | 1   | 1      |

| 1    | 0   | 1      |

| 1    | 1   | 1      |

011+011+

(a) Logic symbol

(b) Truth Table

Tnnuta

Fig.2: A two-input OR Gate

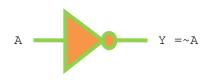

# NOT GATE (INVERTER)

A NOT gate, also called an inverter, has only one input and one output. It is a device whose output is always the complement of the input. Therefore, the output of a NOT gate assumes a logic 1 if its input is logic 0 and vice-versa. The logic symbol and the truth table of a NOT gate is shown in Fig.3.

| Output |

|--------|

| Y=~A   |

| 1      |

| 0      |

|        |

(a) Logic symbol (b) Truth Table

Fig.3: A NOT Gate

#### UNIVERSAL GATES

Though logic circuits of any complexity can be realized by using the three basic gates AND, OR and NOT, there are two universal gates NAND and NOR. Any logic circuit can be implemented by either NAND or NOR gates.

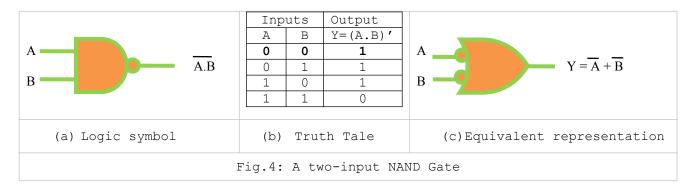

#### NAND GATE

A NAND gate is the combination of AND followed by NOT. The symbol and the truth table of a NAND gate are shown in Fig.4.

# NAND gate as a bubble OR gate

Truth table of the two-input NAND gate reveals that the output is 1 if either of the inputs or both are 0. Or in other words, output is 1 when either A'=1 or B'=1 or both A' and B' are 1 which is the characteristics of an OR gate. Thus, a NAND function in positive logic is equivalent to an OR function in negative logic and a NAND gate is called a bulled OR gate or a negative OR gate. This can be expressed mathematically as,

$$Y = \overline{A \cdot B} = \overline{A} + \overline{B}$$

# NAND gate as an OR gate

If we apply bubble inputs to a NAND gate, the expression of the output of the NAND becomes,

$$Y = \overline{A \cdot B} = A + B = A + B$$

Therefore, bubbled NAND gate is equivalent to an OR gate.

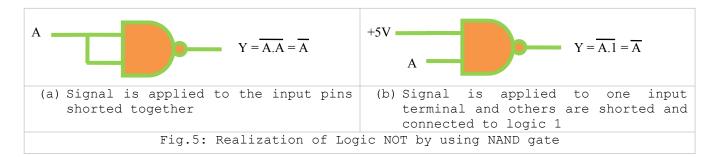

# NAND gate as inverter

A NAND gate can be used as an inverter by shorting its inputs and applying the input signal to the common terminal or by connecting all the inputs except one to the logic 1 and applying the signal to it as shown in Fig.5.

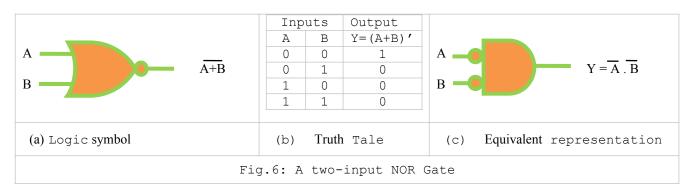

## NOR GATE

A NOR gate is the combination of an OR followed by a NOT gate. The symbol and the truth table of a NAND gate is shown in Fig.6.

# NOR gate as a bubble AND gate

Truth table of the two-input NOR gate reveals that the output is 1 if and only if both the inputs are 0 which is the characteristics of an AND gate. Thus a NOR function in positive logic is equivalent to an AND function in negative logic and thus a NOR gate can be called a bulled AND gate or a negative AND gate. This can be expressed mathematically as,

$$Y = \overline{A + B} = \overline{A} \cdot \overline{B}$$

# NOR gate as an AND gate

If we apply bubble inputs to a NOR gate, the expression of the output of the NOR becomes,

$$Y = \overline{\overline{A} + \overline{B}} = \overline{\overline{A}} \cdot \overline{\overline{B}} = A \cdot B$$

Therefore, a bubbled NOR gate is equivalent to an AND gate.

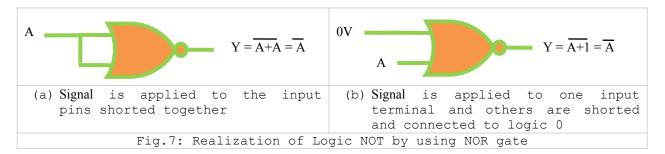

# NOR gate as inverter

A NOR gate can also be used as an inverter like a NAND gate by shorting its inputs and applying the input signal to the common terminal or by connecting all the inputs except one to the logic 0 and applying the signal to it as shown in Fig.7.

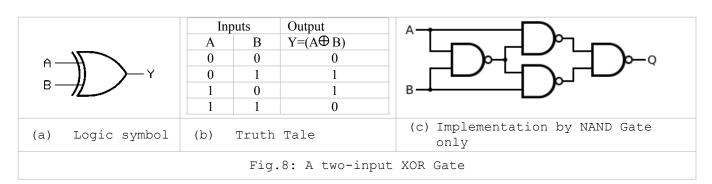

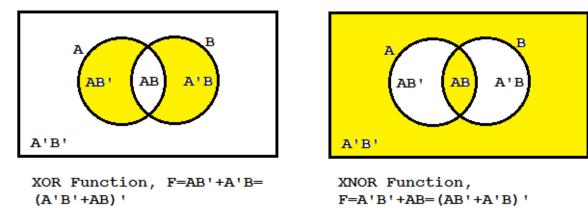

#### XOR Gate

An Exclusive OR (XOR) gate has two inputs and one output. The output assumes logic 1 if one and only one of the inputs assumes logic 1. If both the inputs are either 0or 1, the output is 0. A way to remember the XOR gate is "one or the other but not both". XOR represents the inequality function, i.e., the output is HIGH (1) if the inputs are not alike otherwise the output is LOW (0). XOR can also be viewed as addition modulo 2. As a result, XOR gates are used to implement binary addition in computers. A half adder consists of a XOR gate and an AND gate.

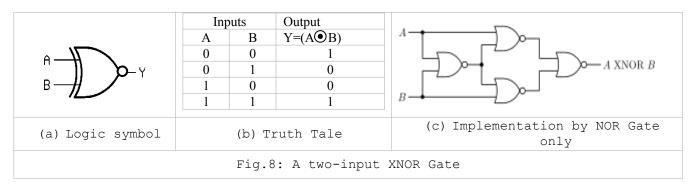

#### XNOR Gate

The XNOR gate is a digital logic gate whose function is the inverse of the XOR gate. The two-input version implements logical equality, behaving according to the truth table. A HIGH output (1) results if both inputs to the gate are the same. If one but not both inputs are HIGH (1), a LOW output (0) results.

# Important

XOR is called an odd function as its output assumes logic 1, if odd numbers of inputs assume logic 1 and XNOR is called an even function as its output assumes logic 1 when even numbers of inputs assume logic 1.

## **BOOLEAN ALGEBRA**

# Axioms and Laws of Boolean Algebra

Axioms or postulates of Boolean Algebra are a set of logical expressions that we accept without proof and based on these postulates useful theorems are built. Actually, the axioms are nothing but the definitions of three basic logic operations AND, OR and NOT. Each axiom is actually the outcome of an operation performed by a logic gate.

| logic gate.                                                                              | -                               | 1 1                        |

|------------------------------------------------------------------------------------------|---------------------------------|----------------------------|

| AND Operation                                                                            | OR Operation                    | NOT operation              |

| Axiom 1: $0.0 = 0$                                                                       | Axiom 5: $0 + 0 = 0$            | Axiom 9: $1' = 0$          |

| Axiom 2: $0.1 = 0$                                                                       | Axiom 6: $0 + 1 = 1$            | Axiom 10: $0' = 1$         |

| Axiom 3: $1.0 = 0$                                                                       | Axiom 7: $1 + 0 = 1$            |                            |

| Axiom 4: 1.1 = 1                                                                         | Axiom 8: $1 + 1 = 1$            |                            |

| Complementation Laws:  If A = 0, then A' = 1  If A = 1, then A' = 0  (A')' = A           |                                 |                            |

| AND Laws: A . 0 = 0 A . 1 = A A . A = A A . A' = 0                                       |                                 |                            |

| OR Laws:<br>A + 0 = A<br>A + 1 = 1<br>A + A = A<br>A + A' =1                             |                                 |                            |

| Commutative Laws: A + B = B + A A . B = B . A                                            |                                 |                            |

| <b>Associative Laws:</b> (A + B) + C = A + (B + C) (A . B) . C = A . (B . C)             |                                 |                            |

| Distributive Laws: A (B + C) = AB + AC A + BC = (A + B) (A + C) Proof: RHS = (A+B) (A+C) | ) = AA+AC+BA+BC = A+AC+BA+BC    | = A(1+C+B)+BC = A+BC = LHS |

| Redundant Literal Rule (RLR                                                              | ):                              |                            |

|                                                                                          | (A+A')(A+B), using distribut    | ive Law                    |

| A (A' + B) = AB<br>Proof: LHS = $A(A' + B) = AB$                                         | = A+B = RHS $AA'+AB = AB = RHS$ |                            |

| Absorption Laws: A+AB = A A(A+B) = A                                                     |                                 |                            |

| Consensus Theorem (Included  1. AB + A'C + BC = AB + A'C  Proof:                         | •                               |                            |

LHS = AB+A'C+BC = AB+A'C+BC(A+A') = AB+A'C+ABC+A'BC = AB(1+C)+A'C(1+B)

= AB + A'C = RHS

```

This theorem can be extended to any number of variables. Like

AB + A'C + BCD = AB + A'C

LHS = AB + A'C + BCD = AB + A'C + BC + BCD = AB + A'C + BC(1+D) = AB + A'C + BC = AB + A'C = RHS.

2. (A+B) (A'+C) (B+C) = (A+B) (A'+C)

Proof:

LHS = (A+B) (A'+C) (B+C) = (AA'+AC+BA'+BC) (B+C) = ACB+ACC+BA'B+BA'C+BBC+BCC = ACB+AC+BA'+BA'C+BC = AC+BA'+BC

RHS = (A+B) (A'+C) = AA'+AC+BA'+BC = AC+BA'+BC = LHS

Transposition Theorem:

AB + A'C = (A+C) (A'+B)

```

```

AB + A'C = (A+C) (A'+B)

Proof: RHS = (A+C) (A'+B) = AA'+AB+A'C+BC = 0+AB+A'C+BC (A+A')

= AB+A'C+ABC+A'BC = AB (1+C)+A'C (1+B) = AB + A'C = LHS

```

# De Morgan's Theorem

Law 1:  $(A + B)' = A' \cdot B'$ Law 2: (AB)' = A' + B'

# Duality Principle:

An OR logic in +ve logic becomes an AND logic in -ve logic and vice-versa. Positive and negative logics thus give rise to a basic duality in all Boolean identities. Also changing from one logic to another, 0 becomes 1 and 1 becomes 0. Thus from a Boolean identity, we can produce the dual identity by changing all '+' signs to '.' signs, all '.' signs to '+' signs and complementing all 0's and all 1's but the variables are not complemented.

```

Relation between complement and dual Let us consider a function f as: f(A, B, C, .....) Then the complement of the function may be written as: f(A, B, C, .....) = f(A, B, C, .....) = f(A, B, C, .....) = f(A', B', C', .....) The dual of the function f can be defined as: f(A, B, C, .....) = f(A', B', C', .....) = f(A', B', C', .....)

```

The first relation states that the complement of a function can be obtained by complementing all the variables in the dual function. Similarly the second relation states that the dual can be obtained by complementing all the literals in the function. Some dual identities are given below:

| Expression                  | <u>Dual</u>               |

|-----------------------------|---------------------------|

| 0' = 1                      | 1' = 0                    |

| 0 . 1 = 0                   | 1 + 0 = 1                 |

| 0 . 0 = 0                   | 1 + 1 = 1                 |

| $A \cdot 0 = 0$             | A + 1 = 1                 |

| A . 1 = A                   | A + 0 = A                 |

| $A \cdot A = A$             | A + A = A                 |

| A . A' = 0                  | A + A' = 1                |

| A . B = B . A               | A + B = B + A             |

| A . (B . C) = (A . B) . C   | A + (B + C) = (A + B) + C |

| $A \cdot (B + C) = AB + AC$ | A + B.C = (A + B) (A + C) |

| $A \cdot (A+B) = A$         | A + AB = A                |

| (AB)' = A' + B'             | (A + B)' = A'B'           |

# Representation in SOP and POS forms

Any Boolean expression can be simplified in many different ways resulting in different forms of the same Boolean function. All Boolean expressions, regardless of their forms, can be converted into one of two standard forms; the sum-of-product form and the product-of sum forms. Standardization makes the evaluation, simplification and implementation of Boolean expression more systematic and easier.

#### The Sum of Product (SOP) Form

Writing functions in SOP form means that the inputs of each term are multiplied using AND function, then all terms are added together using OR function. The variables in each term are not necessarily all the variables of the function. For example, a SOP of F(A,B,C) may contain a term that contains only the variable A but not B nor C, in such case the term is not in its standard SOP form. Standard SOP term must contain all the variables. Boolean algebra states that X+X' =1, then any nonstandard product term may be multiplied X+X' for any missing literal X without affecting its value.

#### Example:

The following function is written in the SOP form:

```

F(A,B,C) = A+BC'+A'BC

```

The inputs to the function F are A, B and C. In each term the inputs are ANDed then all terms are ORed to form the function F. Note that the last term A'BC contains all the inputs of the function (A, B and C), so, this term is written in standard form. But the second term BC' is not in standard form because the input A does not exist, then multiply it by (A'+A). The same is done for the remaining term as follows:

```

F(A,B,C) = A(B+B')(C+C') + BC'(A+A') + A'BC = ABC+ABC'+AB'C'+AB'C'+ABC'+A'BC'+A'BC'

```

From Boolean algebra, (A+A=A) then all similar terms in the equation will be reduced to one term. Now the function F becomes

F(A,B,C) = ABC + ABC' + AB'C + AB'C' + A'BC' + A'BC

#### The Product of Sum Form (POS)

Writing functions in POS form means that the inputs of each term are Added together using OR function and then all terms are multiplied together using AND function. The variables in each term are not necessarily all the variables of the function. For example, a POS of F(A,B,C) may contain a term that contains only the variable A but not B nor C, in such case the term is not in its standard POS form. Standard POS term must contain all the function variables. Boolean algebra states that X.X'=0, then if the term is added to (X.X'), it becomes in the standard POS form, but its value is not affected.

# Example

The following function is written in the POS form: F(A,B,C) = A.(B+C').(A'+B+C')

The inputs to the function F are A, B and C. In each term the inputs are ORed then all terms are ANDed to form the function F. Note that the last term (A'+B+C') contains all the inputs of the function (A, B and C), so, this term is written in standard form. But the second term (B+C') is not in standard form because the input A does not exist, then add (A'.A). The same is done for the remaining term as follows:

```

F(A,B,C) = [A+(B.B')+(C.C')].[(B+C')+(A.A')].(A'+B+C')

F(A,B,C)=[(A+B+C).(A+B+C').(A+B'+C).(A+B'+C')].[(A+B+C').(A'+B+C')].(A'+B+C')

```

From Boolean algebra, (A.A=A) then all similar terms in the equation will be reduced to one term. Now the function F becomes

#### Minterms

Writing a function in its minterm format is equivalent to writing the function in its standard SOP format such that the value of the function at these terms is 1. So that if we have the truth table relating the input variables to the function F, then we can determine which cases result in F=1 and write the minterm form of the function.

#### Maxterms

Writing a function in its maxterm format is equivalent to writing the function in its standard POS format such that the value of the function at these terms is 0. So that if we have the truth table relating the input variables to the function F, we can determine which cases result in F=0 and write the maxterm form of the function.

# Minimization of logic expressions by algebraic method

Every Boolean expression must be reduced to as simple form as possible before implementation to reduce hardware cost as well as to reduce time delay. Laws of Boolean algebra must be utilized while reducing a Boolean expression. The following steps are useful for reduction of expression.

- a) Remove parenthesis

- b) Drop all the identical terms except one. For example, AB+AB+AB+AB = AB

- c) A term containing a literal and its complement may be dropped. For example, A.B.B' = A.0 = 0

- d) Two terms those are identical except for one variable which is missing in one term, the larger term may be dropped. For example, ABC'D + ABC' = ABC'(D+1) = ABC'

- e) Two terms having some literals those are present in true form in one and in complemented form in the other, they can be combined to a single term by dropping those literals. For example, ABCD + ABCD' = ABC (D+D') = ABC.1 = ABC.

#### **EXAMPLES:**

```

AB' + A(B + C)' + B(B + C)'

= AB' + AB'C' + BB'C'

= AR'

_____

[AB'(C + BD) + A'B']C

= [AB'C+AB'BD+A'B']C

= AB'CC+A'B'C

= AB'C+A'B'C

= B'C

A'BC + AB'C' + A'B'C' + AB'C + ABC

= A'BC + ABC + AB'C' + A'B'C' + AB'C

= BC+B'C'+AB'C

= C(B+AB')+B'C'

= C[(B+A)(B+B')]+B'C'

= C(A+B)+B'C'

= AC + BC + B'C'

______

XYZ+YYZ+Y'Z+XY'

= XYZ+YZ+Y'Z+XY'

= YZ+Y'Z+XY'

= Z+XY'

______

[(AB'C)(AB')'+BC]'